Hyper -threading - Hyper-threading

Hyper-Threading (viralliselta nimeltään Hyper-Threading-tekniikkaa tai HT teknologian ja lyhennettä HTT tai HT ) on Intelin n oma samanaikainen säikeistystekniikkaa (SMT) täytäntöönpano käytetään parantamaan parallelization laskennan (tekee useita tehtäviä samanaikaisesti) suoritetaan x86 mikroprosessorit. Se otettiin käyttöön Xeon -palvelin prosessorit helmikuussa 2002 ja Pentium 4 työpöydällä prosessorit marraskuussa 2002. Sen jälkeen, Intel on sisällytetty tätä tekniikkaa Itanium , Atom , ja Core 'i' sarja suorittimia, mm.

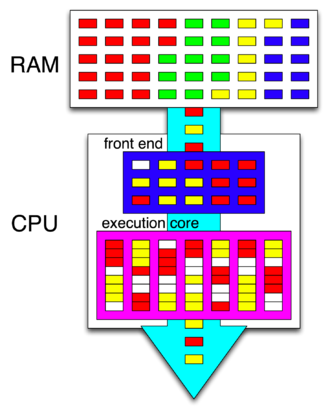

Käyttöjärjestelmä käsittelee jokaista fyysisesti läsnä olevaa suoritinydintä varten kaksi virtuaalista (loogista) ydintä ja jakaa työmäärän keskenään, kun se on mahdollista. Hyper-threadingin päätehtävä on lisätä riippumattomien käskyjen määrää prosessissa; se hyödyntää superskalaarista arkkitehtuuria, jossa useat ohjeet toimivat rinnakkain erillisellä datalla . HTT: ssä yksi fyysinen ydin näkyy käyttöjärjestelmän kahdena prosessorina, mikä mahdollistaa kahden prosessin samanaikaisen ajoittamisen ydintä kohden. Lisäksi kaksi tai useampi prosessi voi käyttää samoja resursseja: Jos resursseja yhdelle prosessille ei ole käytettävissä, toinen prosessi voi jatkua, jos sen resurssit ovat käytettävissä.

Sen lisäksi, että hyperkierteyttämistä tarvitaan samanaikaisesti usean säikeen tukemiseksi käyttöjärjestelmässä, sitä voidaan käyttää oikein vain käyttöjärjestelmällä, joka on erityisesti optimoitu sille.

Yleiskatsaus

Hyper-Threading Technology on Intelin esittelemä samanaikainen monisäikeinen tekniikka, kun taas Sun Microsystems on patentoinut tekniikan taustalla olevan konseptin . Arkkitehtuurisesti Hyper-Threading-tekniikalla varustettu prosessori koostuu kahdesta loogisesta prosessorista ydintä kohden, joista jokaisella on oma prosessorin arkkitehtoninen tila. Jokainen looginen prosessori voidaan pysäyttää, keskeyttää tai ohjata suorittamaan tietty lanka itsenäisesti toisesta loogisesta prosessorista, jolla on sama fyysinen ydin.

Toisin kuin perinteinen kahden suorittimen kokoonpano, joka käyttää kahta erillistä fyysistä prosessoria, hyperkierteisen ytimen loogiset prosessorit jakavat suoritusresurssit. Näitä resursseja ovat suoritusmoottori, välimuistit ja järjestelmäväyläliitäntä; resurssien jakaminen sallii kahden loogisen prosessorin työskennellä keskenään tehokkaammin ja mahdollistaa loogisen prosessorin lainata resursseja pysähtyneeltä loogiselta ytimeltä (olettaen, että molemmat loogiset ytimet liittyvät samaan fyysiseen ytimeen). Prosessori pysähtyy odottaessaan lähettämiään tietoja, jotta se voi lopettaa nykyisen säikeen käsittelyn. Hyperkierteitetyn tai moniydinsuorittimen käytön hyöty riippuu ohjelmiston tarpeista ja siitä, kuinka hyvin se ja käyttöjärjestelmä on kirjoitettu prosessorin hallintaan tehokkaasti.

Hyper-threading toimii kopioimalla tiettyjä suorittimen osia-ne, jotka tallentavat arkkitehtonisen tilan- mutta eivät päällekkäisiä suoritusresursseja . Tämä sallii hyperlankaprosessorin esiintymisen tavallisena "fyysisenä" prosessorina ja ylimääräisenä " loogisena " prosessorina isäntäkäyttöjärjestelmässä (HTT: stä tietämättömät käyttöjärjestelmät näkevät kaksi "fyysistä" prosessoria), jolloin käyttöjärjestelmä voi ajoittaa kaksi säiettä tai prosessit samanaikaisesti ja asianmukaisesti. Kun suoritusresursseja ei käytetä nykyisessä tehtävässä prosessorissa ilman hyperkierteyttämistä, ja varsinkin kun prosessori on pysähtynyt, hyperkierteillä varustettu prosessori voi käyttää näitä suoritusresursseja toisen ajoitetun tehtävän suorittamiseen. (Prosessori voi pysähtyä johtuen välimuistin , haara misprediction , tai data riippuvuus .)

Tämä tekniikka on läpinäkyvä käyttöjärjestelmille ja ohjelmille. Vähimmäismäärä, joka vaaditaan Hyper-threadingin hyödyntämiseksi, on symmetrinen moniprosessointituki (SMP) käyttöjärjestelmässä, koska loogiset prosessorit näyttävät erillisiltä standardiprosessoreilta.

On mahdollista optimoida käyttöjärjestelmän käyttäytyminen usean prosessorin hyperkierteittämistä tukevissa järjestelmissä. Tarkastellaan esimerkiksi SMP-järjestelmää, jossa on kaksi fyysistä prosessoria, jotka ovat molemmat hyperkierteisiä (yhteensä neljä loogista prosessoria). Jos käyttöjärjestelmän säikeiden ajastin ei ole tietoinen hyperkierteistä, se kohtelee kaikkia neljää loogista prosessoria samalla tavalla. Jos vain kaksi säiettä voidaan ajaa, se voi halutessaan ajoittaa kyseiset säikeet kahdelle loogiselle prosessorille, jotka sattuvat kuulumaan samaan fyysiseen prosessoriin; että prosessorista tulisi erittäin kiireinen, kun taas toinen olisi joutokäynnillä, mikä johtaisi huonompaan suorituskykyyn kuin on mahdollista aikatauluttamalla säikeet eri fyysisille prosessoreille. Tämä ongelma voidaan välttää parantamalla ajastinta käsittelemään loogisia prosessoreita eri tavalla kuin fyysisiä prosessoreita; tietyssä mielessä tämä on rajoitettu muoto ajoituksen muutoksista, joita vaaditaan NUMA -järjestelmille.

Historia

Edward S. Davidson ja Leonard kirjoittivat ensimmäisen julkaistun artikkelin, joka kuvaa yleiskäyttöisessä tietokoneessa nykyään hyperkierteittämistä. E.Shar vuonna 1973.

Denelcor, Inc. esitteli monisäieominaisuuksia kanssa heterogeeninen Element Processor (HEP) vuonna 1982. HEP putki voinut olla useita ohjeita samaan prosessiin. Vain yksi tietyn prosessin käsky annettiin olla meneillään milloin tahansa. Jos tietyn prosessin ohje estää putken, muiden prosessien ohjeet jatkuvat putkilinjan tyhjennyksen jälkeen.

Yhdysvaltain patentti hyper-threading-tekniikalle myönnettiin Kenneth Okinille Sun Microsystemsissä marraskuussa 1994. Tuolloin CMOS- prosessiteknologia ei ollut riittävän kehittynyt mahdollistamaan kustannustehokkaan toteutuksen.

Intel otti käyttöön hyperlangat x86-arkkitehtuurissa vuonna 2002 Foster MP -pohjaisen Xeonin kanssa . Se sisällytettiin myös 3,06 GHz: n Northwood-pohjaiseen Pentium 4 -laitteeseen samana vuonna, ja se säilyi ominaisuutena kaikissa Pentium 4 HT-, Pentium 4 Extreme Edition- ja Pentium Extreme Edition -prosessoreissa siitä lähtien. Intel Core & Core 2 -prosessorilinjat (2006), jotka menestyivät Pentium 4 -mallilinjassa, eivät käyttäneet hyperkierteitystä. Core-mikroarkkitehtuuriin perustuvissa prosessoreissa ei ollut hyperkierteitystä, koska Core-mikroarkkitehtuuri oli vanhemman P6-mikroarkkitehtuurin jälkeläinen . P6 -mikroarkkitehtuuria käytettiin aiemmissa Pentium -prosessorien iteraatioissa, nimittäin Pentium Pro , Pentium II ja Pentium III (sekä niiden Celeron & Xeon -johdannaiset tuolloin).

Intel julkaisi Nehalem-mikroarkkitehtuurin (Core i7) marraskuussa 2008, jossa hyper-threading teki paluun. Ensimmäisen sukupolven Nehalem -prosessorit sisälsivät neljä fyysistä ydintä ja skaalautuivat tehokkaasti kahdeksaan säikeeseen. Siitä lähtien sekä kaksi- että kuusiytiminen malli on julkaistu, skaalaamalla neljä ja kaksitoista lankaa. Aiemmat Intel Atom -ytimet olivat järjestyksessä olevia prosessoreita, joilla oli toisinaan hyperkierteytyskyky, pienitehoisille kannettaville tietokoneille ja edullisille pöytätietokoneille. Itanium 9300 käynnistettiin kahdeksan lankaa prosessori (kaksi säiettä ydintä kohti) tehostamalla hypersäikeistys-. Seuraavassa mallissa, Itanium 9500 (Poulson), on 12-laajuinen ongelma-arkkitehtuuri, jossa on kahdeksan suoritinydintä ja tuki kahdeksalle muulle virtuaaliselle ytimelle hyperkierteityksen avulla. Intel Xeon 5500 -palvelinsirut käyttävät myös kaksisuuntaista hyperkierteitystä.

Suorituskykyvaatimukset

Intelin mukaan ensimmäisessä hyperkierteittämistoteutuksessa käytettiin vain 5% enemmän muotti-aluetta kuin vertailukelpoisessa ei -kierteitetyssä prosessorissa, mutta suorituskyky oli 15–30% parempi. Intel väittää jopa 30% parempaa suorituskykyä verrattuna muuten identtiseen, ei-samanaikaiseen monisäikeiseen Pentium 4: een. Tom's Hardware toteaa: "Joissakin tapauksissa P4, joka toimii 3,0 GHz: n taajuudella ja HT on päällä, voi jopa voittaa P4: n, joka toimii 3,6 GHz: n HT: llä sammutettu." Intel väittää myös merkittäviä suorituskyvyn parannuksia Hyper-threading-yhteensopivalla Pentium 4 -prosessorilla joissakin tekoälyalgoritmeissa.

Kaiken kaikkiaan hyperkierteityksen suorituskykyhistoria oli alussa sekava. Eräs kommentti korkean suorituskyvyn tietojenkäsittelystä marraskuusta 2002 toteaa:

Hyper-Threading voi parantaa joidenkin MPI- sovellusten suorituskykyä , mutta ei kaikkia. Riippuen klusterin kokoonpanosta ja mikä tärkeintä, klusterissa käynnissä olevan sovelluksen luonteesta, suorituskyvyn paraneminen voi vaihdella tai olla jopa negatiivinen. Seuraava askel on käyttää suorituskykytyökaluja ymmärtääksesi, mitkä alueet vaikuttavat suorituskykyyn ja mitkä alueet heikentävät suorituskykyä.

Tämän seurauksena suorituskyvyn parannukset ovat hyvin sovelluskohtaisia; kuitenkin, kun ajetaan kahta ohjelmaa, jotka vaativat suorittimen täyden huomion, voi itse asiassa tuntua siltä, että yksi tai molemmat ohjelmat hidastuvat hieman, kun Hyper-Threading-tekniikka kytketään päälle. Tämä johtuu siitä , että Pentium 4: n uusintajärjestelmä sitoo arvokkaita suoritusresursseja ja tasoittaa suoritinresurssit kahden ohjelman välillä, mikä lisää vaihtelevaa suoritusaikaa. Pentium 4 "Prescott" ja Xeon "Nocona" -prosessorit saivat uusintajonon, joka lyhentää toistojärjestelmän tarvittavaa suoritusaikaa ja voittaa suorituskykyrangaistuksen kokonaan.

Intelin marraskuussa 2009 tekemän analyysin mukaan hyperkierteityksen suorituskykyvaikutukset lisäävät yleistä latenssia, jos säikeiden suorittaminen ei johda merkittävään kokonaisnopeuden kasvuun, joka vaihtelee sovelluksen mukaan. Toisin sanoen yleinen käsittelyn viive kasvaa merkittävästi hyperkierteityksen vuoksi, ja negatiiviset vaikutukset pienenevät, koska samanaikaisia säikeitä on enemmän, jotka voivat tehokkaasti hyödyntää hyperkierteityksen tarjoamaa lisälaitteiston resurssien käyttöä. Samanlainen suorituskykyanalyysi on saatavana hyperlangan vaikutuksista, kun sitä käytetään verkkoliikenteen hallintaan liittyvien tehtävien käsittelyyn, kuten verkkoliitäntäohjainten (NIC) tuottamien keskeytyspyyntöjen käsittelyyn . Toinen paperi väittää, ettei suorituskykyä paranneta, kun keskeytyskäsittelyssä käytetään hyperlankaa.

Haitat

Kun ensimmäiset HT-prosessorit julkaistiin, monia käyttöjärjestelmiä ei ole optimoitu hyperlangatekniikalle (esim. Windows 2000 ja Linux, jotka ovat vanhempia kuin 2.4).

Vuonna 2006 hyperkierteyttämistä kritisoitiin energiatehokkuudesta. Esimerkiksi erikoistunut pienitehoinen CPU-suunnitteluyritys ARM totesi, että samanaikainen monisäikeinen voi käyttää jopa 46% enemmän virtaa kuin tavalliset kaksisydämiset mallit. Lisäksi he väittivät, että SMT lisää välimuistin hyökkäystä 42%, kun taas kaksoisydin johtaa 37%: n laskuun.

Vuonna 2010 ARM sanoi, että se saattaa sisällyttää samanaikaisen monisäikeistymisen tuleviin siruihinsa; tämä kuitenkin hylättiin heidän vuoden 2012 64-bittisen mallinsa hyväksi.

Vuonna 2013 Intel hylkäsi SMT : n Silvermont- suoritinytimien suorittamisen epäjärjestyksessä , koska he havaitsivat, että tämä antoi paremman suorituskyvyn ja paremman tehon kuin pienempi määrä ytimiä SMT: llä.

Vuonna 2017 paljastettiin, että Intelin Skylake- ja Kaby Lake -suorittimissa oli virhe, kun ne ottivat käyttöön hyperlangat, jotka voivat aiheuttaa tietojen menetyksen. Myöhemmin julkaistiin mikrokoodipäivityksiä ongelman ratkaisemiseksi.

Coffee Laken myötä Intel alkoi vuonna 2019 luopua hyperkierteittämisestä Core i7 -pöytäprosessoreissa lukuun ottamatta huippuluokan Core i9 -osia tai Pentium Gold -suorittimia. Se alkoi myös suositella hyperlangoituksen poistamista käytöstä, kun paljastettiin uusia suorittimen haavoittuvuushyökkäyksiä , joita voitaisiin lieventää poistamalla HT käytöstä.

Turvallisuus

Toukokuussa 2005 Colin Percival osoitti, että Pentium 4: n haitallinen säie voi käyttää ajoituspohjaista sivukanavahyökkäystä seuratakseen toisen säikeen muistin käyttömalleja , joiden kanssa se jakaa välimuistin, jolloin salaustiedot voidaan varastaa. Tämä ei itse asiassa ole ajoitushyökkäys , koska haitallinen säie mittaa vain oman suorituksensa ajan. Mahdollisia ratkaisuja tähän ovat prosessori, joka muuttaa välimuistin poistoistrategiaansa tai käyttöjärjestelmä estää samanaikaisen suorittamisen eri oikeuksilla varustetuille säikeille samalla fyysisellä ytimellä. Vuonna 2018 OpenBSD- käyttöjärjestelmä on poistanut hyperlangat käytöstä "välttääkseen tietojen vuotamisen sovelluksista muihin ohjelmistoihin" Foreshadow/L1TF- haavoittuvuuksien vuoksi. Vuonna 2019 joukko haavoittuvuuksia johti siihen, että tietoturva-asiantuntijat suosittelivat hyperlangoituksen poistamista käytöstä kaikilla laitteilla.

Katso myös

Viitteet

Ulkoiset linkit

- Intel esittelee Breakthrough Processor Designin , lehdistötiedote elokuusta 2001

- Intel-yleiskatsaus Hyper-threadingista

- Hyper-threading MSDN Magazine -lehdessä

- johdantoartikkeli Ars Technicalta

- US -patentin numero 4 847 755

- Merom, Conroe ja Woodcrest menettävät HyperThreadingin

- ZDnet: Hyperthreading vahingoittaa palvelimen suorituskykyä, sanovat kehittäjät

- ARM ei ole HyperThreading -fani - hahmottaa SMT -ratkaisujen ongelmat

- Hyper-Threadingin vaikutus prosessorin resurssien käyttöön tuotantosovelluksissa